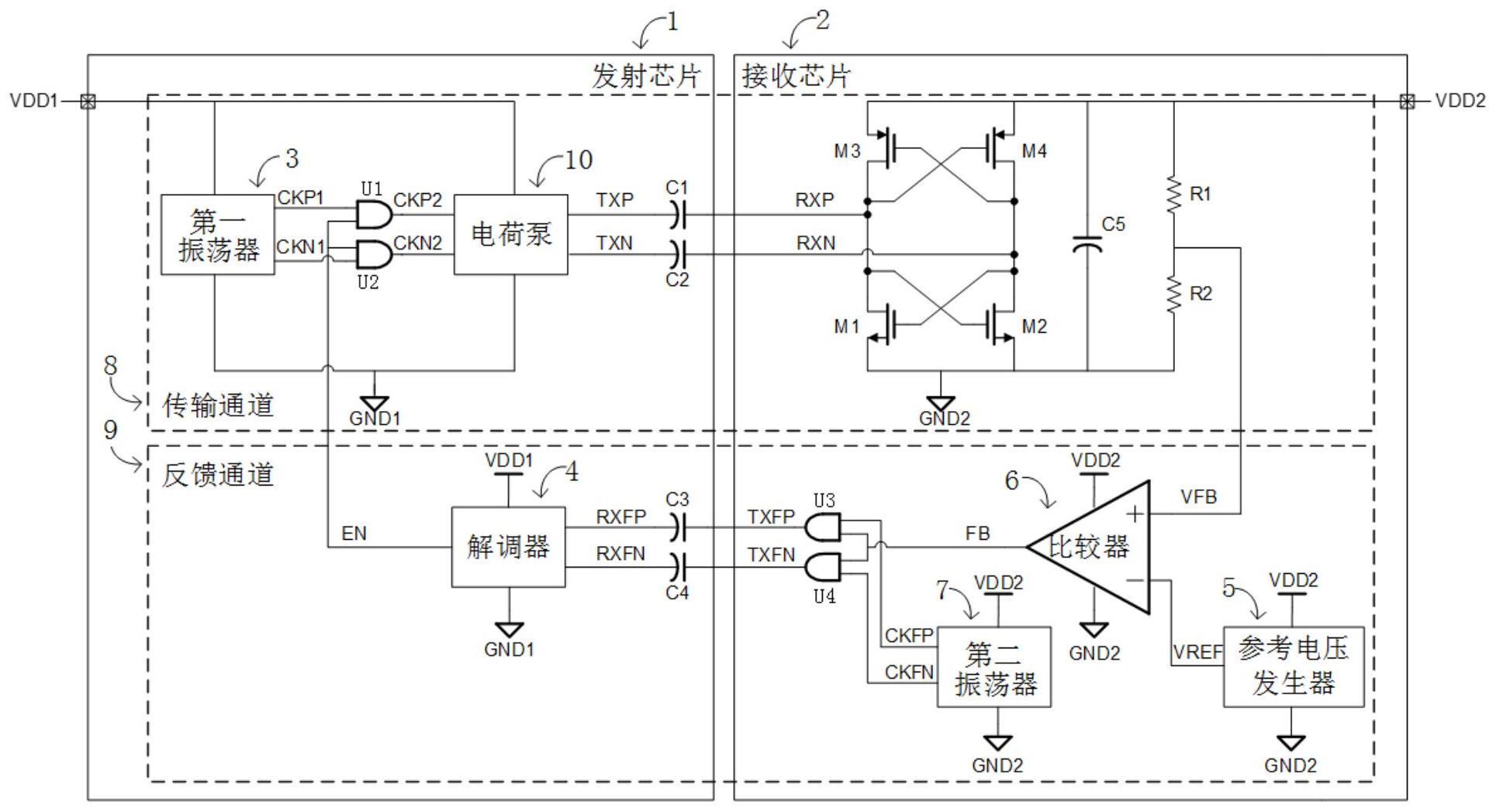

NOVOSENSE has obtained a patent for an isolated power supply chip and its implementation method, improving the integration of the chip

Article Source:China National Intellectual Property Administration | Author:Financial Sector | Issuing Time:2024.05.24